RS sprožilec Načelo delovanja RS-sprožilca. Shema

RS-sprožilec je preprost kontrolni stroj, običajno izveden v obliki digitalnega elektronskega vezja, ki spada v razred sekvenčnih vezij. Kot je znano, v digitalnih vezjih funkcionalne naprave zaporednega tipa vključujejo registre, števce, generatorje števil in kontrolne avtomate, vključno z sprožilci različnih vrst.

Postavite sprožilce v digitalno vezje

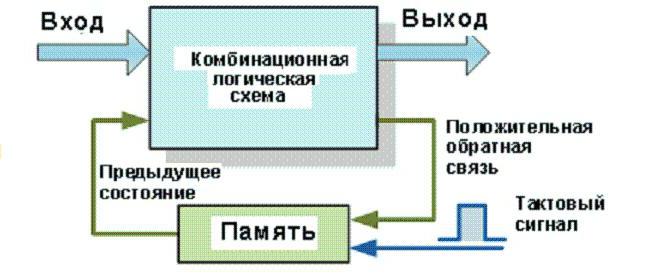

Za razliko od kombinacijskih logičnih vezij, ki spreminjajo stanje glede na dejanske signale, ki se nanašajo na njihove vhode v določenem času, ima zaporedna logika neko obliko vgrajenega "spomina", tako da lahko upoštevajo tako prejšnje kot dejansko stanje svojih vhodov. in izhodov. Spodaj je prikazan splošni blok shema zaporedne naprave.

RS-sprožilec kot digitalni krmilni avtomat vključuje dejanski pomnilnik in kombinacijsko krmilno vezje na tipičnih jezikovnih elementih, ki izvajajo svoj vhodni logični algoritem. Če menimo, da je to vezje uporabljeno za najpreprostejša sprožilna vezja, potem nimajo strukturiranega pomnilnika v obliki neke vrste specializiranega mikrovezja ali vozlišča vezja. Sprožilni pomnilnik obstaja na nivoju funkcije, kot da bi bil vgrajen v algoritem kombinacijske sheme. Izraz tega »spomina« je tako imenovana bistabilnost sprožilca, katerega izhodi so lahko v enem od dveh osnovnih stanj: logični enoti (v nadaljevanju - 1) ali logični ničli (v nadaljevanju - 0). Sprožilec zapomni stalne vrednosti svojih izhodov ("zaskoči") in shrani, dokler ne pride do naslednje spremembe v vhodnih signalih.

Razvrstitev

Če so standardni logični elementi gradniki kombinacijskih vezij, so bistabilna vezja, vključno z RS flip-flopom, glavne komponente za izgradnjo zaporednih logičnih naprav, kot so registri za shranjevanje podatkov, registri premikov, pomnilniške naprave ali števci. V vsakem primeru se lahko upoštevani sprožilci (seveda, kot vsa zaporedna vezja) izdelajo iz naslednjih osnovnih tipov:

1. Asinhroni RS-sprožilec - vezje, ki spremeni stanje takoj, ko se spremenijo vhodni signali. Za tip zadevnih naprav gre za signale na informacijskih vhodih R (reset) in S (namestitev). V skladu z ustaljeno prakso se ustrezni vhodni podatki imenujejo enaki kot signali na njih.

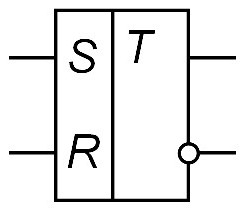

2. Sinhroni RS-prožilec, krmiljen statično , katerega delo je sinhronizirano z nivojem določenega signala ure.

3. Sprožilec po zahtevku 2 z dinamičnim krmiljenjem , ki je sinhroniziran z trenutki nastanka front (ali razpok) urnega signala.

Torej, če se spremembe stanja izhoda pojavijo samo v prisotnosti signala ure, ki se vnaša v ločen urni vhod C, je sprožilec sinhron. V nasprotnem primeru je to vezje asinhrono. Za vzdrževanje svojega trenutnega stanja sekvenčna vezja uporabljajo povratne informacije, to je prenos dela izhodnega signala na njegov vhod.

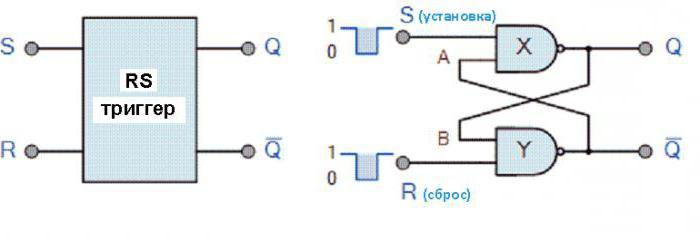

RS-sprožilec na logičnih elementih

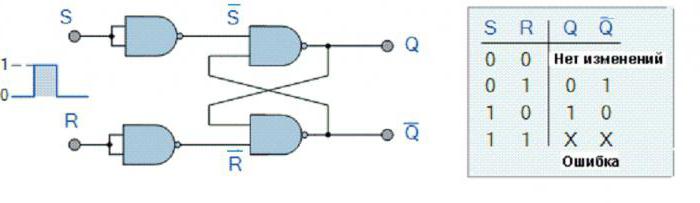

Najenostavnejši način je združiti par logičnih elementov NAND z dvema vhodoma. V tem primeru se povratna informacija iz izhoda enega elementa prenese na vhod drugega (glejte spodnji diagram).

Praviloma so v tej shemi vhodni signali prikazani kot inverzni (s podčrtano), čeprav je kasneje pri analizi dela uporabljen zapis neposrednih (neinvertiranih) vhodov. Zaradi tega je zelo težko razumeti logiko sprožilca. Zato ne bomo uvajali inverzije vhodov v fazi obravnave delovanja vezja na elemente NAND, temveč bomo to upoštevali v prihodnosti, ko bo spremenjena.

Koliko vhodov in izhodov ima RS sprožilec? Iz zgornjega diagrama je razvidno, da vsebuje S-vhod in R-vhod, ki služita za nastavitev in ponovno nastavitev tokokroga, kot tudi neposredne Q in inverzne Q̃ izhode. Toda ta najpreprostejši sprožilec se nanaša na asinhroni tip, njegov simbol pa je prikazan spodaj.

V sinhroni napravi je tudi vhod C za urne impulze.

Stanje "nameščeno"

Poglejmo, kako RS-flip-flop deluje v tem stanju, ki ga podajajo vrednosti R = 0 in S = 1. Ker je vhod 0 elementa AND-NO Y nivo 0, potem je Q̃ = 1 (logika AND-NO). Iz izhoda Y se signal Q back vrne tudi nazaj k elementu X (vhod "A"). Ker je S = A = 1, je Q = 0.

Če je nastavljen R = 1 in je vhod S še vedno 1, potem imamo na vhodih Y B = 0 in R = 1, njegov rezultat pa je Q̃ = 1, se torej ni spremenil. Torej, če je S = 1, potem RS shema sprožilca "snaps" v "Installed" stanje Q = 0 in Q̃ = 1, in spreminjanje signala R ne spremeni.

Stanje "Ponastavi"

V tem drugem ustaljenem stanju, Q̃ = 0, in Q = 1, in je definiran z vhodi R = 1 in S = 0. Ker ima element X vhod S = 0, njegov rezultat je Q = 1 (logika AND-NOT). Signal Q se vrne nazaj k elementu Y (vhod "B"), in ker je R = B = 1, potem je Q̃ = 0.

Če S postane enak 1, ko R = 1, potem Q̃ ostane enako log 0, to pomeni, da se ne spremeni. Torej, pri R = 1, se sprožilno vezje spet »zapre« v stanju »Ponastavitev« Q̃ = 0 in Q = 1, shranjeno s katerimkoli signalom S.

Rezultate v preglednici povzamemo

Stanje Q in Q̃ signalov lahko določimo z naslednjo tabelo resnice:

| Stanje | S | R | Q | Q̃ | Opis |

| Namestitev | 1 | 0 | 0 | 1 | Izhod Q̃ = 1 |

| 1 | 1 | 0 | 1 | brez sprememb | |

| Ponastavi | 0 | 1 | 1 | 0 | Izhod Q̃ = 0 |

| 1 | 1 | 1 | 1 | brez sprememb | |

| Neveljaven | 0 | 0 | 1 | 1 | stanje napake |

Vidimo lahko, da sta S = R = 1 Q in Q̃ lahko enaka 1 ali 0 (vendar ne istočasno!) Odvisno od ravni S ali R vhodov pred nastankom tega stanja izhodov. Tako se pri pogojih S = R = 1 stanja izhodov Q in Q Q ne more spreminjati. Spremeni se lahko samo, če na eni od vhodov spremenite raven od 1 do 0.

Vrednost S = R = 0 je nezaželen ali nesprejemljiv pogoj in se ga je treba izogibati. Stanje S = R = 0 povzroči, da sta oba izhoda Q in Q̃ nastavljena na raven 1, stanje Q̃ pa mora biti vedno nazaj na Q. Posledica je, da sprožilec izgubi nadzor nad Q in Q if, in če dva vhoda zdaj gredo v stanje 1, vezje postane nestabilno in preklopi v nedefinirano stanje.

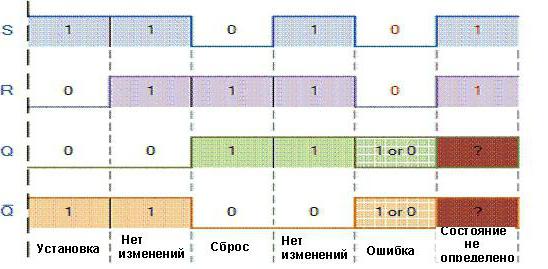

Tabela stikala RS-Trigger

Kar je bilo povedano v prejšnjem oddelku, je ponazorjeno z naslednjim prehodnim vzorcem.

Kot lahko vidite, se pri S = R = 0 pojavi neravnovesje (negotovost) izhodnega stanja. To lahko vodi do preklopa enega od izhodov hitreje od drugega, zaradi česar se sprožilec preklopi na eno ali drugo stanje, ki morda ne sovpada z zahtevanim, in podatki se bodo poškodovali. To nestabilno stanje se običajno imenuje meta-stabilno.

Tako se lahko podoben sprožilni zapah prenese v stanje "Installed" z vnosom 0 na S-vhod (če je na R-vhodu 1) in se prenese v stanje "Reset" z uporabo 0 na R-vhod (če je 1 na S-enter). Sprožilec vstopi v nedefinirano stanje (meta-stabilno), če se na oba vhoda hkrati uporabi raven 0.

Preklapljanje stanja izhodov poteka z majhno zakasnitvijo glede na spremembo signala na enem od vhodov brez uporabe urnega signala. Zato je zgornja shema asinhroni RS-sprožilec.

Spremenite prožilno shemo

Kot smo videli zgoraj, osnovni elementi IS-NOT obravnavanega RS-flip-flopa delujejo tako, da ko je nastavljen, Q̃ = 1 in Q = 0, in ko je resetiran, Q̃ = 0 in Q = 1, čeprav bi bilo bolj logično imeti Q v prvem stanju = 1, v drugem pa Q = 0. V tem primeru se tudi izkaže, da se sprememba stanja pojavi, ko se nivo signala spusti z 1 na 0.

Zato je treba za pravilno delovanje sprožilnega vezja obrniti vhodne signale. Nato se preklopi na stanje, ko uporabimo pozitivne vhodne signale. V ta namen dodajte v vezje dva dodatna elementa IS-NOT, ki sta povezana z vhodoma S̃ in R̃, kot je prikazano na spodnji sliki. Tukaj so vhodi elementov AND-NOT že predstavljali inverzne vhodne signale.

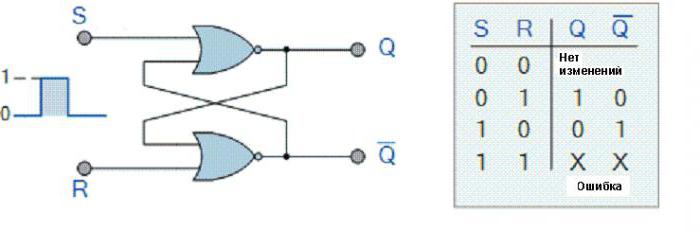

Tako kot pri uporabi elementov AND-NOT lahko zgradite preprost RS-sprožilec z uporabo dveh elementov OR-NOT, ki sta povezani na enak način. Delovalo bo enako kot zgoraj opisana shema NAND. Istočasno je aktivna visoka raven signalov na vhodih in nesprejemljiv pogoj, ko se na obeh vhodih uporabi logična raven "1", kot je prikazano v tabeli resnice na spodnji sliki.

Kako sinhronizirati sprožilec

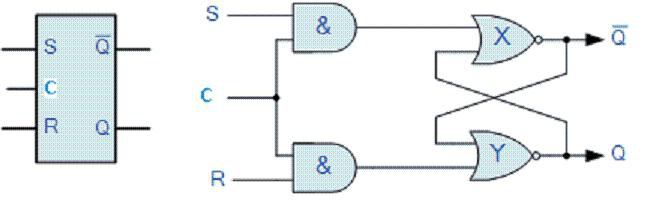

Včasih je zaželeno imeti bistabilni sprožilec v zaporednih logičnih vezjih, ki spremeni svoje stanje, ko so izpolnjeni določeni pogoji, ne glede na stanje S ali R vhodov. Takšna shema se lahko ustvari s povezovanjem elementa z dvema vhodoma in zaporedoma z vsakim vhodom sprožilca. Kombinacija dveh vhodov elementov In, dobimo nov vnos sprožilca. Dodajanje pomeni, da izhodi Q in Q vhod spreminjata stanje, ko je signal na njem visok, zato ga lahko uporabimo kot uro C-input, kot je prikazano na spodnji sliki.

Kadar je signal na vhodu C na ravni 0, so izhodi obeh elementov tudi na ravni 0 (logika elementa And), ne glede na stanje dveh vhodov S in R, oba izhoda Q in Q̃ pa sta "zaklenjena" v zadnjem ustaljenem stanju. Ko se signal na vhodu C spremeni v nivo 1, se tokokrog odzove kot običajen bistabilni sprožilec in postane pregleden za nastavitev in ponastavitev stanja.

Ta dodatni C-vhod se lahko priključi tudi na izhod generatorja urne frekvence, nato pa na sinhronski RS flip-flop. Ta shema tako deluje kot standardni zapiralni mehanizem, ki se lahko aktivira, vendar se izhodi aktivirajo le, ko se nivo C vnese na vhod C in so onemogočeni, ko se pojavi logična ničelna raven.

Sprožilni registri

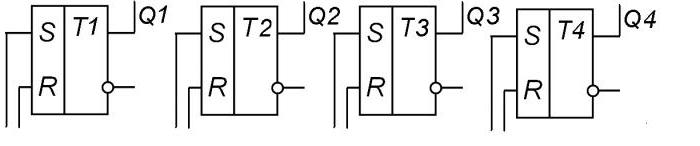

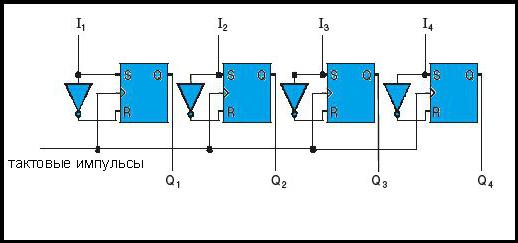

RS sprožilec lahko shrani 1 bit digitalnih informacij. Če je potrebno shraniti več bitov, na primer digitalno binarno besedo več binarnih bitov (v mikrokontrolerjih, običajno 8 ali 16), se lahko sprožilci povežejo vzporedno in tvorijo registre. To so najenostavnejše naprave za začasno shranjevanje niza binarnih digitalnih številk, v katerih vsak sprožilec shrani vrednost ene številke (0 ali 1. to je en bit). 4-bitni register, prikazan spodaj na flip-flopih RS, vsebuje štiri ločene flip-flop-e.

Vsako binarno število od (0000) 2 do (1111) 2 se lahko shrani v ta register samo z nastavitvijo ali ponastavitvijo ustreznega sprožilca. Predpostavimo, da je prvi sprožilec nastavljen (Q1 = 1), drugi je ponastavljen (Q2 = 0), tretji je tudi resetiran (Q3 = 0), četrti pa je nastavljen (Q4 = 1). Nato binarno število, zapisano v register, bo (1001) 2.

Poleg vzporednih registrov, ki so namenjeni shranjevanju digitalnih besed, se na RS flip-flopih izdelajo tako imenovani prestavni registri, pri katerih se številke digitalne besede zaporedoma s prihodom vsakega urnega impulza premaknejo levo ali desno za en bit. Spodaj je prikazan diagram takšne naprave na sinhronih sprožilcih.

Takšni registri se uporabljajo v vezjih za serijski vmesnik, ko se digitalne besede, ki prihajajo iz krmilnega krmilnika, prenesejo malo v komunikacijsko linijo.